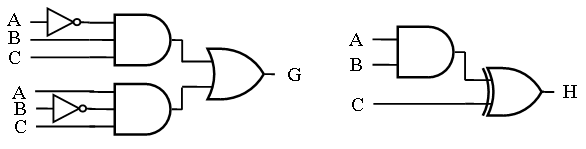

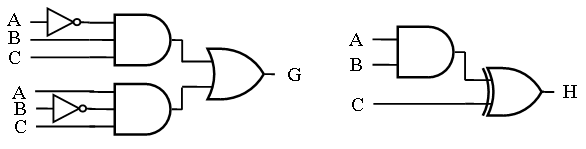

module 1st_exam(A,B,C,D,F) inputs A, B, C; Output D, F; and g1(E,B,C); not g2(d,E,A); OR g1(F,B,C); endmodule;

Your report should include Verilog log and simulations where required.

module 1st_exam(A,B,C,D,F) inputs A, B, C; Output D, F; and g1(E,B,C); not g2(d,E,A); OR g1(F,B,C); endmodule;

Maintained by John Loomis, last updated 1 Sept 2005