Download: project files

The conversion of frequency to phase increment requires the multiplicative constant:

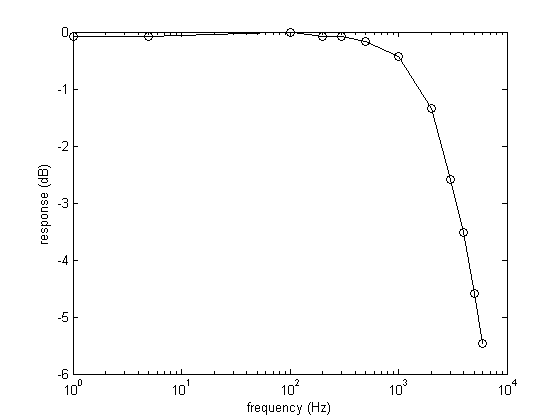

Actual frequencies will be very slightly smaller than the desired frequency. For example, a desired frequency of 15 kHz measured 14999.85 kHz, compared to a predicted value of 14999.995

//set up DDS frequency

//Use switches to set freq

wire [31:0] dds_incr;

wire [31:0] freq = SW[3:0]+10*SW[7:4]+100*SW[11:8]+1000*SW[15:12]+10000*SW[17:16];

assign dds_incr = freq * 91626 ; //91626 = 2^32/46875 so SW is in Hz

reg [31:0] dds_phase;

always @(negedge AUD_DACLRCK or negedge DLY_RST)

if (!DLY_RST) dds_phase <= 0;

else dds_phase <= dds_phase + dds_incr;

wire [7:0] index = dds_phase[31:24];

sine_table sig1(

.index(index),

.signal(audio_outR)

);

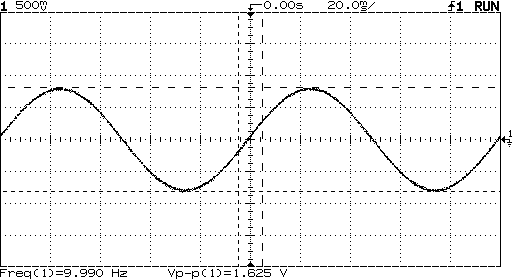

10 Hz

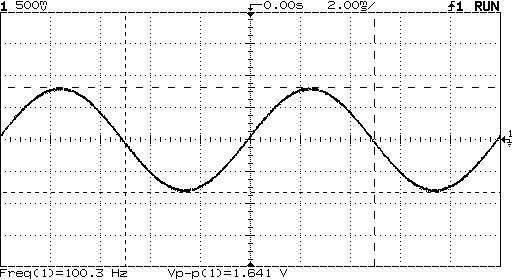

100 Hz

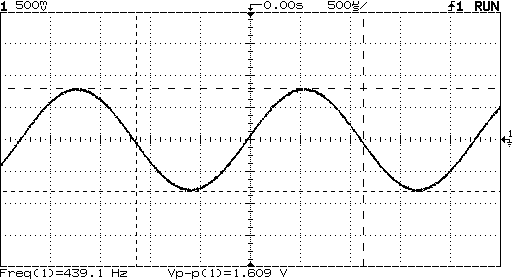

440 Hz

15 kHz

Verilog source and Quartus reports

National Instruments, Understanding Direct Digital Synthesis (DDS), (pdf)

Maintained by John Loomis, last updated 11 March 2008